C. D. Thompson

# DEPARTMENT of COMPUTER SCIENCE Carnegie-Mellon University A Complexity Theory for VLSI

by August 1980

CMU-CS-80-140

#### A Complexity Theory for VLSI

Dissertation presented to

Carnegie-Mellon University

Computer Science Department

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

by C. D. Thompson August1980

This research is supported in part by the National Science Foundation under Grant MCS 78-236-76 and a graduate fellowship, and in part by the Office of Naval Research under Contract N00014-76-C-0370.

ABSTRACT

PAGE 1

#### **Abstract**

The established methodologies for studying computational complexity can be applied to the new problems posed by very large-scale integrated (VLSI) circuits. This thesis develops a "VLsI model of computation" and derives upper and lower bounds on the silicon area and time required to solve the problems of sorting and discrete Fourier transformation. In particular, the area A and time T taken by any VLSI chip using any algorithm to perform an N-point Fourier transform must satisfy  $AT^2 = cN^2log^2N$ , for some fixed c > 0. A more general result for both sorting and Fourier transformation is that  $AT^2X = (N^2 + xlog^2xN)$  for any x in the range O < x < 1. Also, the energy dissipated by a VLsI chip during the solution of either of these problems is at least  $(N^2 + xlog^2xN)$ . The tightness of these bounds is demonstrated by the existence of nearly optimal circuits for both sorting and Fourier transformation. The circuits based on the shuffle-exchange interconnection pattern are fast but large:  $T = O(log^2N)$  for Fourier transformation,  $T = O(log^3iV)$  for sorting; both have area A of at most  $O(N^2/log^1)^2A^2$ . The circuits based on the mesh interconnection pattern are slow but small:  $T = O(N^1)^2 log log N$ ,  $A = O(Z') log^2 NJ$ .

Keywords: Computational complexity, information theory, graph embedding, mesh connections, shuftle-exchange connections, parallel algorithms, sorting, Fourier transformation, VLSI, area-time complexity.

PAGE 1 TABLE OF CONTENTS

#### **Table of Contents**

| 1.                                                         | Introduction                                     | <b>'3</b> |

|------------------------------------------------------------|--------------------------------------------------|-----------|

|                                                            | 1.1 Units of area, time, information, and energy | 6         |

|                                                            | 1.2 Problem definitions                          | 9         |

|                                                            | 1.2.1 Discrete Fourier transformation            | 10        |

|                                                            | 1.2.2 Sorting                                    | 12        |

|                                                            | 1.3 Notation                                     | 13        |

|                                                            | 1.4 Related work                                 | 13        |

| 2.                                                         | The VLSI model of computation                    | 19        |

|                                                            | 2.1 Lower bounds                                 | 22        |

|                                                            | 2.2 Correspondence to Visi' chips                | 28        |

|                                                            | 2.3 Upper bounds                                 | 41        |

|                                                            | 2.4 Relation to the model of Mead and Rem        | 48        |

| 3.                                                         | Lower bounds                                     | 51        |

|                                                            | 3.1 Minimum bisection width                      | 52        |

|                                                            | 3.2 Area                                         | 54        |

|                                                            | 3.3 Time bounds                                  | 60        |

|                                                            | 3.3.1 Discrete Fourier transformation            | 67        |

|                                                            | 3.3.2 Sorting                                    | 73        |

| 4.                                                         | Upper bounds                                     | 77        |

|                                                            | 4.1 Algorithms                                   | 78        |

|                                                            | 4.2 Recirculation algorithms                     | 84        |

|                                                            | 4.3 VLSI implementations of the FF1'             | 85        |

|                                                            | 4.3.1 Performing the FF1' on a mesh              | 85        |

|                                                            | 4.3.2 The multiply-add cell                      | 90        |

|                                                            | 4.3.3 The FF1 on shuffle-exchange connections    | 98        |

|                                                            | 4.3.4 Area bounds for the shuffle-exchange graph | 104       |

|                                                            | 4.4 Vi.si implementations of sorting             | 108       |

|                                                            | 4.4.1 Sorting on shuffle-exchange connections    | 108       |

|                                                            | 4.4.2 The comparison-exchange cell               | 110       |

|                                                            | 4.4.3 Sorting on mesh connections                | 112       |

|                                                            | 4.5 Constant factors in the VLsI implementations | 116       |

|                                                            | Conclusion                                       | 119       |

| Appendix A. Control program for cell 0 of a mesh-based FFT |                                                  |           |

|                                                            | 123                                              |           |

|                                                            | Circuit                                          | on        |

| PAGE 2 A COMPLEXITY THEORY F                               |                                                  | OR VLSI   |

INTRODUCTION PAGE 3

### Chapter 1 ~nt rod uct~on

Very large-scale integrated (VLsI) circuit technology has proroundly changed the size and speed of computing structures. A VLsI microcomputer occupies less than a square centimeter of silicon, yet outperforms several cubic feet of twenty-year-old computer components. The circuit densities attainable with VLSI are already staggering, and further improvements lie on the horizon. Chips with one hundred thousand transistors are feasible today. This figure may well increase to ten or twenty million in the next decade [Mead 80].

The computational power of a chip is often measured by the number of transistors it contains. This is a misleading approach, for the organization of a chip's circuitry has a very strong effect on its size and speed. In general, the more regular chip designs make more efficient use of silicon area. Such designs use less area for the wiring between transistors, leaving more room for the transistors themselves. This explains why present-day technology can put one hundred thousand transistors on a memory chip but only ten thousand transistors on a "random logic" chip. it also indicates that circuit size is more naturally measured by area than by counting transistors.

This thesis explores the relation between the speed and size of VLSI circuits, using the methodology of complexity theory. The first step in this methodology is to devise an accurate and precisely-defined model of a VLSI chip. It is then possible to derive limits on the area and time performance of any chip built according to the rules of the model. This thesis proves both upper and lower bounds on VLSI chip performance. A sample lower bound is that any chip that performs an N-point

PAGE 4 A COMPLEXITY THEORY FOR VLSI

Fourier transform in time T must have an area A large enough to satisfy  $AT^2 \_cN^2log^2N$ , for some fixed c > 0. The cofresponding upper bound is obtained by designing a chip that can solve a Fourier transform. The designs presented in this thesis are nearly optimal in their  $AT^2$  performance, demonstrating that there is not much room for improvement in either the upper or the lower bounds.

The use of a new model of computation in this thesis is justified by the novel aspects of VLSI design. As indicated above, the size of a VLSI chip is best measured by its area. The useful area of a chip is devoted to transistors and wires; neither can be neglected in a realistic model. Unfortunately, Turing machines and other traditional models of computation lack the concept of wire area. Yet it is precisely this concept that is used in Chapter 3 to prove lower bounds on area-time performance.

The main results of this thesis are expressed as area-time tradeoffs. The product of chip area A with the square of the time T it takes to perform an N-element Fourier transform or sorting problem must satisfy  $AT^2 = c2(iN^2log^2AT)$ . That is,  $AT^2 = cN^2log^2N$  for some fixed c > 0 and  $N > N_0$ . This lower bound is nearly the best possible, in the sense that there exist both fast, large chips and slow, small chips that nearly achieve these bounds. The small chips solve their problems in time proportional to  $N^{l} = log log N$ , using area proportional to  $iVlog^2IV$ . The nearoptimality of these designs is immediate, since their  $AT^2$  performance exceeds the lower bound quoted above by a factor of only  $O(log log \sim The fast chips are also near-optimal. The Fourier transform chip operates in <math>O(iog^2iV)$  time, while an analogous design solves a sorting problem in  $O(ilog^3A9)$  time. Both chips occupy  $O(N^2 log^{-1})^2 A9$  area.

A more general result bounds the performance of any chip with area A that takes time T to solve an N-element sorting or Fourier transformation problem:

$AT^2X = \sim (Nl \sim log^2 xN_s)$ , for all x such that  $0 < x \sim 1$ . Each value of x corresponds to a utility function  $AT^2X$  with slightly different weights given to area INTRODUCTION PAGE 5

and time performance. The lower bound on  $AT^2$  performance given above is merely a special case (x = 1) of this general result.

The general lower bound implies that a chip with performance A = O(N) and T = O(N) and T = O(N) would be optimal under any  $AT^2X$  metric, O < X < I. The slow, small chips described above come quite close to these performance figures. The fast and large chips are far from optimal in this general sense. They only approach optimality when X is nearly I, that is, when time is much more important than area.

The following section discusses units of measurement of VLsI circuits from a physical standpoint. The product of chip area with time is shown to be a measure of energy, leading to the following corollary of the general lower bound result: at least  $\sim 2(N^3)^{-2} log N$  units of energy must be dissipated during the sorting or Fourier transformation of N numbers on a VLSI chip.

The remainder of the current chapter (Sections 1.2 through 1.4) is devoted to a definition of the problems of sorting and Fourier transformation, the establishment of

some notational conventions, and a review of the relevant literature.

Chapter 2 develops a "VLsI model of computation" as a basis for the derivation of lower and upper hounds on chip performance. The notion of a "communication graph" is introduced as the formal analog of a VLSI chip. Communication graphs correspond to VLsI chips, according to the scheme described in this chapter.

Lower bounds are the subject of Chapter 3. A key parameter of any communication graph is defined, its "minimum bisection width." The minimum bisection width of a communication graph determines lower hounds on the area and speed of its corresponding VLSI chip. In brief, the area A of a chip is at least proportional to the square of the width of its communication graph,  $w^2$  The maximum-possible speed of a chip also increases with its width; more precisely,  $T = WN \log N / w$ . Multiplying the first inequality by the square of the second gives the lower bound  $AT^2 = 2(tV^2\log^2 N)$ . With the additional assumption that the area A is at least Q(N), the relation becomes  $AT^2X = 2((N+w^2))(N+w^2)$ .

PAGE 6

A CO~vtPLEXJTY THEORY FOR VLSI

It can be shown that choosing w  $O(N''^2)$  minimizes  $AT^2X$  for 0 < x < 1, leading to the general lower bound  $AT^2X \sim jyl + X/\sim g^2xJy\sim 1$

Chapter 4 develops near-optimal chip designs, providing upper bounds on achievable VLSI performance. Four designs are presented: "fast" and "slow" chips for both the sorting and Fourier transformation problems. The fast chips are based on the shuffle-exchange interconnection pattern, while the slow ones are based on mesh-type connections.

#### 1.1 Units of area, time, information, and energy

A VLSI chip may be thought of as a multi-layered, planar structure. Transistors are formed on the surface of a silicon substrate, and cannot be stacked on top of each other. Above them is one or more layers of interconnect material (often a metal) that is selectively etched away to form connections or wires between the transistors. The conductive layers are normally insulated from each other, so that wires can cross over one another if they are formed in different layers. Wire segments in different layers can be connected to each other, if a "via" or hole is formed in the insulation.

For concreteness, the area calculations of this thesis assume there is only one layer of interconnect material, and that wires are laid out on a rectangular grid. Thus wires may meet only at i-ight angles. Wires may also cross over each other at right angles, if one of them makes a short run in a heavily doped "channel" in the silicon substrate.

The upper and lower bound results of this thesis could be extended to cover chips with multiple layers of interconnection, as indicated by the discussion on page 36 and by Theorem 3: k layers of interconnection decrease chip area by at most a factor of  $k^2$ . There is little immediate importance to such an extension, since current chips use at most two layers of interconnection. Future chips are also likely to liave a small number of layers, due to manufticturing difficulties and costs. Each

INTRODUCTION PAGE 7

additional layer of interconnection requires one or more additional masking steps, to define where the wires are to run. Every manufacturing step contributes to chip cost both directly (because of increased fabrication time) and indirectly (because of reduced yields). Thus VLSI will continue to be essentially planar until radical advances are made in fabrication techniques.

For convenience, the ass umptions of the VLsI model of computation made in this thesis are numbered in order of appearance and collected in a list on page 44. (En this list, each assumption is split into two parts, labelled "L" and "U." Part "U" contains the suppositions strictly necessary for the lower bound proofs, while part "U" contains the additional suppositions needed by the upper bound constructions.) The assumptions made in the previous paragraphs may be summarized as (Li):

horizontal and vertical wires are formed in a single planar layer, although two wires may cross each other at right angles.

There is a natural *unit of area* for VLSI. Manufacturing and physical limitations give rise to a minimal spacing between the centers of parallel wires. In the terminology of Mead and Conway [Mead 80], this minimal spacing is 4X. The square of this length,  $16X^2$ , is thus a convenient area unit. The area of a chip can be expressed in terms of unit squares, leading to (Li, extended): one unit square is just large enough to contain one small transistor or one wire cross-over, and just wide enough to allow one wire to enter through each (unit-length) edge. The 64K RAM currently available has an area of about  $10^6X^2$ , and chips of  $10\sim$  or  $10.9\sim$ 2 may be possible {Mead 79}.

The total area of a VLSI chip may be evaluated in two ways. In production, it is the mask size that is important, that is, the area of the smallest bounding rectangle. This is another important assumption, (U2): the area of a bounding rectangle is used to describe the upper bounds (circuit constructions) of this thesis. On the other hand, the lower bounds derived here measure only the area actually occupied by wires. This is assumption (L2). It strengthens the lower bound results and allows the derivation of bounds on energy dissipation, as noted later in this section.

PAGE 8

*Information* is measured in bits. One bit of information describes the outcome of an event for which there were two equally likely possibilities. For example, a onehit signal can communicate the result of flipping a fair coin (heads or tails). More generally, tile information content of an event that has outcome / with probability  $p \sim is \sim (-p_1 log p \sim)$  bits [Shannon 49]. This quantity is also called the entropy of the probability distribution P.

The unit of *time* is defined by (L3): a unit-width wire has at most unit bandwidth. In other wo~cls, a signal that encodes one bit of information has a duration of at least one time unit. For binary logic, a lower bound on the length of the time unit is the duration of the shortest pulse that can change the state of a circuit.

The definitions of area, time, and information given above are chosen to simplify the theoretical model. Their values in actual implementations will depend on engineering decisions. For example, the unit of time will probably be stretched by a factor of ten or more to allow for propagation delay and synchronization overhead. In any event, the asymptotic results of this thesis will be valid to within a constant factor as long as the definitions of area and time remain fixed. These units of measurement must not change with the size of the circuit being built or with the size Not' the problem being solved.

Unit values for area and time in a currently feasible MOS technology are  $10 \sim m$  and 50 as, respectively [Mead 80]. In other words, wires are at  $10 \sim m$  spacings and the clock signal used for synchronization has a period of 50 as. The units of  $AT^2$  in this case are  $250000 \sim tm^2 ns^2$ . Anticipated advances in technology will reduce unit widths and times by a factor of /0, bringing the  $AT^2$  unit to  $25 \sim un \sim ns^2$ .

A unit of *energy* is defined by the product of the units of area and time. When a signal is sent from one transistor to another, the driver must charge (or discharge) the capacitance presented by both the wire and the receiver. The energy required to charge a capacitor is proportional to its capacitance, so that the energy consumed by a wire or a transistor is proportional to its area (the constant of proportionality INTRODUCTION PAGE 9

depends on the way in which the chip is fabricated). Thus it can be said that one unit of energy is consumed by one unit of chip area every time it is involved in the transmission of a signal.

The proof's of Chapter 3 place a lower bound on the amount of wire that must be active continuously if a circuit is to compute a function in a given time T **The** general lower bound on  $AT^2X$  performance can therefore be used at  $x = \frac{1}{2}$  **to give a** lower hound on the total energy required to compute a function:

$AT = \sim (N^3)^2 \log N$ , for both sorting and Fourier transformation.

The unit of energy for a MOS chip can be evaluated in the following way. Currently, wires have about  $iii\sim$  pF of capacitance per unit area  $(100\ j\sim m^{2})$ . Assuming that the signal voltage swing on a wire is 4 volts,  $.008\ pJ$  of energy  $(=\frac{1}{2}CV^2)$  is needed to charge each unit of wire area, each time its voltage is changed. Thus the product of wire area with the amount of time it is actively transmitting data has the dimensions of energy, and units of  $.008\ pJ$ . This energy unit will be reduced to  $8\ X\ I08\ pJ$ , when lengths, times, and voltages are scaled down by the predicted factor of  $10\ \{Mead\ 801$ .

#### 1.2 Prob'em definitions

The two computational problems treated in this thesis are functions of N variables onto N variables. A VLsI chip is said to solve one of these problems if it can produce the appropriate N output values from any vector of N input values. Input and output values remain on the chip. This assumption is in accordance with a paradigm of comparing a  $V \sim$  sr chip with a conventional computer. Just as mr."~lLy issues can be studied without reference to the I/O devices on a conventional computer, there is no need to model off-chip communication if there is a very large amount of memory on the chip. (The assumption of on-chip computation is implicit in assumptions L6 and L7, as defined in Section 2.i.)

The values for problem variables are chosen from the elements of a finite set.

PAGE 10

A CO~LEXITY THEORY FOR VLSI

That is, the value of a variable may be encoded as a "word" composed of a bounded number of bits. If there are no more than  $7 \sim f$  possible  $\sim$  'alues for each variable, then a word length of  $I^{7}og$  II'!] bits can be used.

A particular assignment of values to input variables constitutes a "problem instance." These values must be chosen independently and uniformly, leading to (L4): there are ~~fNequally likely problem instances, if each of the iVinput variables can take on ~V[ different values. Assumption [4 is more powerful than it may appear at first glance. Its insistence on an independent, uniform distribution of input values allows many algebraic simplifications in the derivation of time bounds, as will be seen in Section 3.3.

A chip is said to solve a problem in *average* time Tif it takes an average of Tunits of time to solve one of the M"~ equally likely problem instances. En a similar fashion, a chip is said to solve a problem in *worst-case* time T if it takes no more than Tunits of time to solve any instance of the problem.

For lower hounds, an average-case result is strictly stronger than an equivalent worst-case result. A chip with an average-case time of at least T must also have a worst-case time of at least T. The lower bound on Fourier transformation covers the average case, while the sorting lower bound applies only to the worst case. Obtaining a lower bound on achievable performance for the average case of a sorting chip remains an open problem.

The upper bound results of this thesis use nonadaptive (straight-line, nonbranching) algorithms, so that the chips operate at the same speed on any problem instance. The best-, average-, and worst-case performances of the chips are thus identical.

#### 1.2.1 Discrete Fourier transformation

The central problem studied in this thesis is the computation of the discrete Fourier transform, or DEl. The DEl may he defined as a matrix-vector INTRODUCTION

PAGE 11

multiplication,  $A \sim 1$  where A is the matrix of constants defined below. The input vector is  $\sim$  and the output vector is  $\sim$  both are of length N. The elements of the N-by-N matrix A are constants determined by tile structure of the ring in which the computation is performed.

A ring is defined by a set of elements and the rules for adding and multiplying elements. The values of variables in ~ and ~ must be chosen from the elements in the ring. For the reason noted in the previous section, there can be only a finite number of values for each of the problem variables. The customary definition of a Fourier transform over the (infinite set) of complex reals is thus inadmissable here; only finite rings will be considered in this **thesis**.

The structure of the ring over which the DFT' is defined has some impact on the properties of the transform. It is customary [Agarwal 75, Alto 74, **Bonneau** 73, Nicholson 71] to restrict attention to commutative rings with additive and multiplicative identity elements, a principal *Nt/i* root of unity, and a multiplicative inverse for N. Such rings lead to DETs with most of the properties associated with Fourier transforms in the field of complex numbers: invertibility, orthogonality, and the cyclic convolution property [Agarwal 75].

A particularly suitable ring for the DFT is the integers [0, 1, Al-i] under addition and multiplication modulo iVI. The prime factorization of the modulus Al characterizes this ring. If

$$\mathbf{Al} \qquad r_1 \sim_7 r_2 Pk \sim. \tag{1.1}$$

then there is an Nth root of unity and an element  $N \sim$  if and only if N divides the greatest

common divisor of [pj -1, P2 - 1] [Agarwal 75, Bonneau 73]. An immediate implication of this result is that Al.> N.

If the constant a is a principal iVt/z root of unity, the matrix A in the defining equation  $\sim =A$  \_is given by

$$Afi,j]=at',forO (1.2~)$$

The elements *A[/, 1J* are all distinct [Agarwal 75].

PAGE 12

A COMPLEXITY TIJEORY FOR VLSI

The length of the transform, N, determines what algorithms may be used to compute a DEl. Winograd's ~Winograd 76] DFT algoi-ithm is based on a recognition of this effect. The upper boLinds of Chapter 4 are implementations of the "fast Fourier transform" or FF1 [Aho 74], and thus assume (U4): N is a power of 2. En contrast, the lower bounds of Chapter 3 apply to all N.

The Fourier transform circuits of Chapter 4 use an additional assumption, also part of (U4):  $log\ iW = O(log\ iV)$ . This assumption allows the value of any input or output variable to be coded in  $O(log \sim bits)$ , so that the dependence of circuit size on Al can be expressed in terms of N alone. An interesting existence question is raised by this assumption. For arbitrary' /V, there had better be a ring modulus Al of appropriate size capable of supporting an iV-element DFT. According to Agarwal's result, cited above, an N-element DFT exists in a ring of prime modulus Al if Al is of the form qN-i-1. Fortunately, it can be shown {Wagstaff' 79, Linnik 44] that the least prime Al of this form is bounded by a polynomial in N. A word-length of  $log\ Al = O(log\ N)$  bits is thus available for any N-element DFT. Assumption U4 merely states that the circuit constructions of Chapter 4 use nearly minimal word-lengths.

#### 1.2.2 Sorting

The N inputs to a sorting chip may be thought of as integers between 0 and Al—i. This analogy to tile integers is intended to convey two things. First, the input values are ntembers of a linearly ordered set, so that a "greater than" relation is defined. Second, there are exactly Al different possibilities for each input valLie.

The N outputs of a sorting chip are a permutation of the inputs into sorted order. That is, output  $y_0$  is the smallest input value, output  $y_1$  is the second smallest, and so forth.

The lower bound of Theorem 15 requires an addition to assumption (L4):

~'[=iV<sup>1~</sup> for some fixed positive. Note that some lower limit must be assumed

INTRODUCTION PAGE 13

for Al in order to obtain a powerful result. For example, the sorting problem for

Al = 1 is trivial; no computation is required to determine that all output values are

0.

#### 1.3 Notation

The following functional notation is used throughout this work.

=  $O('g \sim 'n \sim)$  "fis big 0 of g," an upper bound within a constant factor. There exists a positive constant c for which f('n) = cg(n) for all sufficiently large n.

f(n) = O(g(n)) gis theta of g, "an exact bound within a constant factor. There exist positive constants  $c_1$  and  $c_2$  for which  $c_1 g(n) \sim f(n) < c$ , g(n) for all sufficiently large n.

$f \sim "n \sim$ ) =  $\sim ('g('n \sim "f') \text{ is omega of } g, "a \text{ lower bound within a constant factor. There exists a positive constant } c \text{ for which } f('n) \_ cg('n,) \text{ for all sufficiently large } n.$

[xl] "ceiling of x," the least integer greater than or equal to x.

Lx] "floor of x," the greatest integer less than or equal to x. log x the base two logarithm of x.

$$log^{-3}$$

"x  $(log x)$   $-1$   $log log \sim x$   $(log log \sim x)$

$\mathbf{X}$  the number of elements in the set X or dimensions in the vector

X.

the miumber of distinct values in the sample space of the (discrete) random variable *X*.

#### 1.4 Related work

Three existing areas of inquiry shed light on the problems studied here. First, applications of a theory of *graph embedding* in the plane, such as printed circuit board wire routing, are relevant to the essentially planar VLSI technology. Second, PAGE 14

A COMPLEXITY THEORY FOR VLSI

the model of computation developed here for VLSI is similar in spirit to other *information theoretic models*. Third, the area-time results derived in this thesis may be contrasted with the *space-time tradeoffs* observed in more traditional models of computation.

*Graph embedding.* Results in this area are written in a wide range of styles, from a hard-nosed pragmatic approach to a carefully-formalized theoretical treatment.

On the practical end, the problem of wire and chip placement on printed circuit boards is quite similar to the problem of wire and circuit placement on the surface of VLSI chips. Donath [Donath 79] derives upper bounds for wire length in both problem domains, as a function of a parameter in the empirical "Rent's relationslup" for logic networks. These upper bounds overestimate wire lengths by a factor of two or less, on a number of actual layouts. Sutherland and Oestreicher [Sutherland 73] estimate wiring requirements for printed circuit boards, under the pessimistic assumption that chips are randomly placed on the board. Both studies use the key idea, developed here in Section 3.1, of obtaining analytical results by partitioning the graph.

Formal approaches to graph embedding also yield interesting results. Cutler and Shiloach [Cutler 78] study the problem of embedding bipartite graphs in the plane, under the rather restrictive assumption that no edge "crossovers" are allowed. Lipton and Tarjan [Lipton 77] and Rosenberg ~Rosenberg 79] obtain bounds on the cost of embeddings, under the very liberal assumption (for VLSI) that any **number of** edges may pass over a point. Leiserson [Leiserson 80] uses more natural assumptions in his algorithm for embedding a graph in near-minimal area. The last three papers cited use variants of the partitioning idea alluded to in the previous paragraph. Lipton and Tarjan take the idea one step further, and use the size of the partition to derive complexity results. Much of their work should transfer into the VLSI model of computation, but this task has not yet been attempted.

*Information-theoretic models.* An information-theoretic model is defined here as iNTRODUCTION PAGE 15

one that emphasizes the cost of information transmission. Most existing models have a different orientation, measuring operation counts and memory requirements for the traditional von Neumann architecture for uniprocessors. Even so, the informational

emphasis of the VLSI model of' computation is far from unique.

Among established models in complexity theory, cellular automata [von Neutnann 66] are the most suited for informational studies. Each cell of a twodimensional array of automata changes its state as a function of the current states of its nearest neighbors. From an information-theoretic standpoint, each cell receives a packet of information from its neighbors every time unit. This packet need have no more bits than the logarithm of the number of possible neighborhood state configurations. Minimal time and state solutions to cellular automata problems thus tend to minimize the transmission of information. Moshell and Rothstein's "bus automata" could be used to model the flow of information among cellular automata in a natural fashion [Moshell 76].

Floyd [Floyd 72] makes use of the entropy of a memory state to obtain lower bounds on the number of operations needed to perform memory reorganization in a two-level store. In his model, an operation is the production of a third "page" of information, as any function of the contents of any two pages. If  $n_{II}$  is the number of records (amount of information) to be sent from tile *ith* page to the *jdi* page, the entropy of a memory state is defined as  $\sim nU \log n_{IJ}$ . (Actually, Floyd's V-function is defined somewhat differently to handle the case that  $\log nU$  is not an integer.) One operation can change the entropy of a memory state by at most p, where p is the number of records on a page. A lower bound on the number of operations needed to achieve a reorganization is thus the entropy of the original state (relative to that reorganization) divided by p.

On another front, a theory of "distributed computing" is beginning to emerge as an outgrowth of research into parallel processing for database manipulation. A. Yao [Y ao 79] outlines some of the implications of various assumptions that might be made about a distributed system: one-way vs. two-way communication,

PAGE 16 A COMPLEXITY THEORY FOR VLSI

deterministic *vs.* probabilistic computations. Abelson [Abelson 80a] develops some analytic tools for bounding the information transfer required in the computation of continuous, differentiable functions. Both authors treat a problem as a fixed partitioning of the input data between a pair of processors. In distinction, this thesis defines a problem as an input-output relation, with no partitioning assumptions.

*Space-time tradeoffs*. Although operation counts and memory requirements of uniprocessors are irrelevant considerations for VLSI, the analytical tools to demonstrate space-time tradeoffs in more conventional models can be applied to VLSI area-time studies.

Grigoryev [Grigoryev 76] studies the problem of computing a set of m binary functions. He proves that any straight-line (nonbranching, nonadaptive) algorithm with T steps and S storage locations satisfies ST.>ml/2, if the set of functions is "I-

independent." A similar notion of functional independence is the basis for the bounds of Section 3.3. Grigoryev's definition is discussed in more detail in that section. Savage and Swamy [Savage 79a] generalize Grigoryev's method and apply it to integer multiplication. Earlier, they had found a space-time tradeoff for the fast Fourier transform algorithm [Savage 77].

Space-time bounds are often derived from consideration of a "pebble gathe" [Paterson 70, Savage 77] played on the graph of a straight-line algorithm. Each pebble corresponds to a storage register and each node represents a function to be evaluated. An edge leads from one node to another if the value of the parent appears as a parameter in the child's function. Nodes with no parents correspond to problem inputs; nodes with no children are problem outputs. Placing a pebble on a node means storing the value of the node's function in the pebble's register, which is possible only if the node's parents (the function's parameters) are all pebbled (evaluated and **stored). Removing a pebble from a node corresponds to erasing the** contents of the pebble's register. The object of the game is to pebble all childless nodes, in other words, to evaluate all the problem outputs. Time in this model is measured serially as the number of pebble movements, that is, the number of function evaluations. Space is the number of different pebbles (registers) used. INTRODUCTION

PAGE 17

For VLSI, one is tempted to interpret the graph of an algorithm in quite a different fashion. Each node could be a processor waiting for its predecessors to send it the results of their function evaluations. Time would then be the depth of the graph, and space the area of the graph when embedded in the plane. The pebbling game seems irrelevant in this interpretation of a graph. Some pebbling results, however, involve proofs of necessary properties of any graph for a particular problem. For example, Valiant [Valiant 76] shows that any Fourier transform algorithm corresponds to a hyperconcentrator. Pippenger's extension of this result, as reported by Tompa [Tompa 78], is the basis of Lemma 8 of Section 3.3.1.

Unfortunately, most pebbling results are based on algorithms operating over the set of real numbers. The analytic techniques used do not always transfer into the modular arithmetic, or other finite algebraic structures, of the VLSI model of computation.

PAGE 18

A COMPLEXITY THEORY FOR VLSI

# Ch3pter 2 The VLSI mod& of cornputat~on

A VLSI chip composed of transistors and interconnections is modeled by a network of *nodes* and *wires*. A node represents a transistor or a small cluster of transistors; as such, it receives and transmits signals over its connecting wires. A node may also represent a wire junction, in which case it merely copies the signals it receives on any one of its wires onto its other wires. Nodes and wires thus simulate the actions of transistors and wires on a VLSI chip.

Nodes are capable oIstoring a limited amount of information. This enables them to model data storage elements on a VLSI chip. It also allows a collection of nodes and wires to be a complete, self-contained computing structure. The inputs to a computation are stored in a distinguished set of nodes called *source nodes*. (These correspond to the "input registers" on a VLSI chip.) The output i~alues of a computation are collected in another set of nodes called *sink nodes* (the "output registers" on a chip). A collection of nodes and wires capable of solving a problem is called a *communication graph*. A communication graph is thus the formal analog of a VLSI chip.

Section 2.1 contains precise definitions of the functional capabilities of nodes and wires, and the ways in which they may be put together to form communication graphs. The lower bound proofs of Chapter 3 (which apply to communication graphs) demonstrate that these definitions imply limits on the area and time performance of communication graphs.

Every VLsI chip can be accurately modeled by a communication graph, as shown PAGE 20

A COMPLEXITY THEORY FOR VLSI

by a correspondence scheme described in Section 2.2. For this reason, the lower bound results of Chapter 3 are valid for all VLsI chips as well as for all communication graphs.

In Section 2.3 we turn to issues of upper bounds. An upper bound in the VLSI model of computation implies the existence of a chip achieving the stated performance.

Unfortunately, not all communication graphs defined in Section 2.1 correspond to feasible chip designs. Section 2.3 remedies this difficulty by adding further constraints to the VLSI model of computation. Any communication graph satisfying the additional constraints of Section 2.3 is called an *admissible communication graph*. A generalized MOS process [Mead 80] may be used to implement a feasible chip based on any given admissible communication graph.

Section 2.4 discusses the relationship of the VLSI model of computation with the similar model implicit in the work of Mead and Rem [Mead 79].

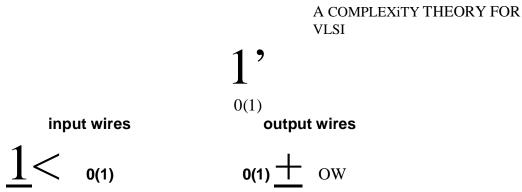

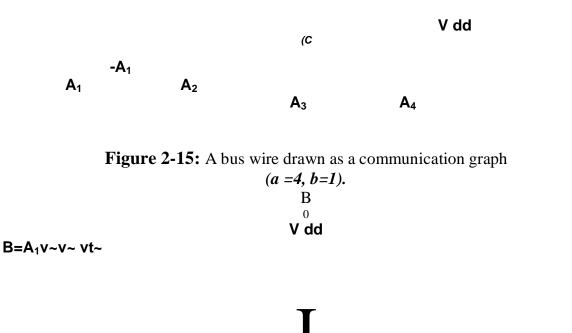

The methodology of this chapter is summarized by the Venn diagram of Figure 2-1. The universe being studied is that of "all computational structures" that fit in area A and solve an N-element problem P in time T. A (possibly empty) set of communication graphs achieving this area-time performance may be constructed in accordance with the definitions of Section 2.1. This set is denoted as

cornfl1ufliCatiofl graphs."

The correspondence scheme of Section 2.2 constnictively demonstrates that a communication graph can be obtained from any VLSI chip. Thus the set of "( $\sim$ \,T,P,N)-VLsI chips" (actually, the set of (A,T,P,N)-communication graphs corresponding to VLSI chips) is a subset of all (A,T,P,N)-communication graphs.

The generalized MOS process adopted for upper bound proofs is of course only one way of building Vr.~si chips, so that "(A,T,P,N)-MOS chips" is a proper subset of "(Aj,P,N)-VLSI chips." Finally, the class of "admissible (A,T,P.N)-communication graphs" defined by Section 2.3 form a subset of "(A.T.P,N)-N1OS chips." according to the correspondence scheme of that section.

THE VLSI MODEL OF COMPUTATION

PAGE 21

This methodology illuminates the type of arguments needed to demonstrate the consistency and utility of the VLsI model of computation. For example, assumption A2 of Section 1.1 defines two measures of the area occupied by a circuit, depending upon whether the area figure is to be used as a lower or upper bound. The lower bound area is just the amount of area occupied by wires, while the upper bound area is that of the smallest bounding rectangle. This dual definition is consistent with the inclusion of "admissible (A,T,P,N)-communication graphs" in "(A,T,P,N)-communication graphs" since any graph bounded by a rectangle of area A must also have fewer than A units of wiring. All computational structures with performance (A,T,PJN)

Figure 2-1: Domains of the lower and upper bound models.

PAGE 22 A COMPLEXITY THEORY FOR VLSI

#### 2.1 Lower bounds

A communication graph is composed of *nodes* and *wires* laid out on a grid of unit squares. Physically, a wire is a horizontal or vertical strip of metal connecting two points on the surface of a chip. A node represents a point at which wires meet, so that a transistor or even a wire junction is a node.

Assumption Li, below, defines the concept of area for the lower bound model of Vi.sr computation. It is a restatement of the unit-area definition given in Chapter 1 on page 7. (Some of the assumptions developed in Chapter 1 applied to lower bounds, some only to upper bounds. Accordingly, each assumption was prefixed with either an "L" or a "U" to indicate its application to lower or upper bounds. Assumptions Li through L8 are defined in this section, forming a complete definition of the lower bound model of computation. Section 2.3 defines the upper bound model as a set of additional restrictions on these assumptions, labeled Ui through U8.)

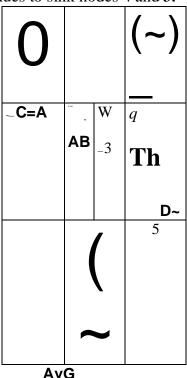

Assumption Li: Area. A unit square can contain one node or one wire crossover. One wire may cross each edge of a unit square, so that nodes have a maximum of four wires.

There are thus nine types of squares occupied by wires, as shown in Figure.2-2. A square may also contain a node, as indicated in the tenth "tile" of this figure. An arrowhead is drawn at the point where a wire meets a node if information flows into the node from that wire. This notion of information flow will be formalized later.

# LII <u>Li</u> R~ Hi [<u>H IH PH ~ LU</u>

Figure 2-2: Wire segments.

Assumption L2 of Section 1.1 (page 7) makes the following definition of the total area of a communication graph. Note that only occupied squares are counted toward the lower bound on area.

THE VLSI MODEL OF COMPUTATION

PAGE 23

Assumption **L2**: Total area. The total area of a communication graph is equal to the number of unit squares occupied by wires or nodes.

Figure 2-3: The shuffle-exchange graph of sixteen nodes, embedded in 58 unit squares (and bounded by a 60-unit rectangle).

The function of a wire is to carry information from node to node. Most wires carry information in one direction only. Such wires are drawn as a (J)ossibly curved) line connecting two nodes, with an arrowhead pointing in the direction of information flow. The rarer bidirectional wire (such as the one in Figure 2-10) is drawn with two arrowheads.

**Example.** Figure 2-3 shows an embedding of the shuffle-exchange graph of sixteen nodes. The shuffle-exchange connectivity is natural for sorting and Fourier transformation [Stone 71]. A shuffle-exchange graph of size N=2'~ has nodes numbered from  $Oto\ N$ —i. Node ican transmit information to node  $(2i + [21/Nj) \mod N)$  over a "shuffle" connection. "Exchange" connections exist in both directions between nodes 21 and

21+1. Section 4.3.4 treats the general problem of embedding a shuffle-exchange graph of size N.

The following assumption bounds the rate at which one-bit signals can pass any point on a wire. This bandwidth limitation defines the unit of time for a communication graph, as indicated in assumption L3.

Assumption L3: Units of time. A wire has at most unit bandwidth in each direction.

Time bounds are obtained in the VLsI model of computation from arguments PAGE 24 A COMPLEXITY THEORY FOR VLSI

based on the bandwidth limitation of wires. For this reason, it is important that a problem be specified in a fixed number of bits. As defined in Section 1.2, a "problem instance" is an assignment of values to input variables. By the following assumption, based on the discussion on page 10, each problem instance cannot be coded in fewer than  $N \log N$  bits. (Strictly speaking, assumption L4 is not a definition of the model so much as a description of the computational problems treated in this thesis.)

Assumption L4: Problem definition. Each of N input variables takes on one of M different values, for a total of MJV equally likely problem instances. In the sorting problem,  $VI = N^{I^{\sim}}$  for some fixed positive e. In the Fourier transform problem, A'f > N.

It is now possible to describe the functionality of nodes and wires. At each instant of time *t* the signal available at one end of wire *A* is expressed by the boolean variable A('t). (Two boolean variables are associated with each bidirectional wire, to denote the possibly different signals available at either end.)

The value of each signal is determined by the *transmission function* of the node that originally placed it onto its wire. The simplest transmission functions describe the operations of nodes with no "state" (local storage, memory). For example, a memorytess node that has three incoming wires (A, B,and  $\sim$ and one outgoing wire (D) has a transmission function of the form

$$D(t + \sim D) = f(A(t), B\sim, C'(t\sim 2).$$

(2.1~)

The boolean variables  $A(t, \sim, B(t))$ , and C'('t) denote the signals on the incoming wires at time 1. The signal on wire D appears at the far end of that wire after some fixed delay '3D > 0. The function f is any of the 256 boolean functions of three hoolean variables. Note that there is no explicit delay associated with the computation of f Any such "node delay" is added to the delays of its wires. Also note that this model allows wires to act as transmission lines: wire D may have unit bandwidth even if its delay  $\sim$  is greater than unity, for there is nothing to keep a node from transmitting another signal before the first one has been received. (No VLSI technology allows transmission lines as yet, hut the VLSI model of computation is ready for them

THE VLSI MODEL OP COMPUTATION

**PAGE 25**

should they become feasible. The motivation for the development of on-chip transmission lines is strong, due to the ever-increasing ratio of propagation delay. to device tcli time.)

Nodes with state can have more complicated transmission tenctions, as defined in Assumption Li

Assumption U: Transmission functions. Node states and wire signals are completely and consistently described by the transmission function associated with each node. A node with state vector 5. input wires (S...,D~andoutputwires~...,G)computesafiznctionofthe!brm

$$(S(t\#l), E(t\#8EA..., C(ti-8g)J = FTS('aga..., D(oj'(22))))$$

where <sup>8</sup>E and <sup>8</sup>G are the non-negative delays of wires Eand G.

There are two extremely important assumptions buried in the lbnnalism of equation (2.2). First, the function *F* is defined on the instantaneous values of its variables: there is no allowance for timing 'litter" or any other synchronization difficulties. Thus the lower bound model of computation assumes that some form of synchronization between nodes is available, for which no area or time charges are made. The subject of synchronization will be discussed in more detail in Section 2.3, as the upper bound model of computation is developed.

A second buried assumption is that of determinism, that the signals coming into each node take on one of two values. Marginal and erroneous signals will appear in any real system, although careful design practice will

reduce the probability of error to nearly zeta In any event, the Vr.si model of computation treats only an ideal world in which there are no transmission errors.

A communication graph is not completely specified without a description of the initial states of all nodes and wires. These states must all be constants, that is, independent of the values of problem input variables, with the exception of one node for each input variable, its *source node*. In other words, all information about the value of each input variable is initially concentrated at one point. As the computation proceeds, this information will of course be diffused throughout the PAGE 26

A COMPLEXITY THEORY FOR VLSI

communication graph. Note that the correspondence between source nodes and input variables is one-to-one. This assumption is crucial to the proofs of Section 3.3, although the recent work of Brent and Kung [Brent 79] indicates that it might be relaxed.

Assumption I.~6: Source nodes. The initial state of a source node may be any function of the value of its input variable. Each input variable affects only the initial state of its source node.

Just as there is one source node for each input variable, there is one *sink node* for each output variable. However, sink nodes need not be in one-to-one correspondence with their variables. The function of a sink node is to collect information about the correct values for its output variables. The computation is complete when each sink node has completely determined the values of its output variables. To ensure that a sink node is not just "guessing" the right answer momentarily, it is required to come to a stable decision, in the sense formalized below.

Assumption L7: Sink nodes. There is a fixed assertion for each sink node, relating its state to the correct values of its output variables (as a function of the values of the input variables). A computation is complete at time T if all assertions are satisfied at all times t = T.

The final assumption of the lower bound model defines what it means to say that a chip solves a problem: it must be able to solve all instances of that problem (assignments of values to input variables).

Assumption LS: Solution time. A communication graph is said to solve a problem in worst-case time *T* if it takes no longer than *T* units of time to complete its computation of any problem instance. A communication graph is said to solve a problem in average time *T* if its average completion time, over all problem instances, is *T*.

Some additional naming and drawing conventions will prove useful when dealing with communication graphs. Nodes that are neither sources or sinks are called *switching nodes*, since they can be considered as mere "switches" ot. combiners of information. This classification of nodes as sources, switches, or sinks for information is not disjoint: a single node may serve in any or all of these capacities.

THE VLSI MODEL OF COMPUTATION

PAGE27

The following conventions are adopted for drawing communication graphs. Nodes are numbered and wires are named withcapital letters. The delay of a wire is either zero or unity, and all wires emanating from a node have the same delay. In the notation of assumption L5, all the  ${}^8E^{\prime} \sim$  for a given node have the same value, either  $\theta$  or 1. Nodes with zero-delay wires are drawn as dots, while nodes with unit-delay wires are drawn as open circles. The logical content of node transmission functions are indicated by boolean equations on each wire.

Example. Figure 2-4 is a communication graph for a Vi.si chip that computes the 'and' and 'or' functions of two boolean variables p and q. Nodes 1 and 2 are sources, node 3 is a switch, and the sink nodes are nodes 4 and 5. Wire A carries information about input p from node 1 to node 3. Similarly, wire B carries the value of input q. Node 3 computes the values of the two outputs, p A q and p V q. Wires C and D carry these output values to sink nodes 4 and 5.

Figure 2-4: A simple communication graph.

A more precise description of Figure 2-4 is contained in the following transmission

functions, initial assignments, and output assertions.

```

j: S_1(t+1)=S_1(t); A(t+1)=S_1('t); S_1(0)=p; A(0)=false

J\sim: S_2(t+1)=S_2(i9; B(t+')=\sim 2(t); S_2(0)=q; B(0)=false j\sim. C(t)==A(t)A B(t);

D(t)=A(t)v B(t); C(0)=D(0)=false j\sim: S_4(t-,-1)=C(i); S_4(0)=false: \underline{assert} S_4('t)=pAq

jj: S_5(t-i-1)=D(t); S_5('O)=false; \underline{assert} S_5(t)=pvq

```

From this description, it may be seen that the communication graph takes two units of time to solve its problem. The initial state  $S\sim(0)$  of PAGE 28

A COMPLEXITY THEORY FOR VLSI

source node I is defined as the value of its input variable p. Wire A carries this value during the first time unit, since  $A(1)=S_I(0)=p$ . In the same fashion, wire B carries the value of q during time t=1. Referring now to Jj, wire C carries p q and wire D carries q q during this same period of time. (Node q is defined to have zero delay, so that these signals are available immediately.) The signals on wires q and q are stored in the states of nodes q and q during time q as indicated by the first equations in q and q. The output assertions will be satisfied for all times q so that the computation is complete after two time units.

Note that nodes l, l, 4 and l have unit delay and that node l has zero delay. This might be an appropriate model for a circuit that clocks its inputs at time t=l and clocks its output latches at l=l. The next section discusses the subject of appropriate models in more detail.

The delays of nodes 4 and 5 can be reduced without violating the lower bound model of computation. However, the delays of nodes I and 2 must remain, to avoid sending two signals down wires A and B at the same time. (The initial value on wire A is *fuse*; a zero-delay transmission function for node I would also require I(Q)=p.) Thus the computation of the 'and' and 'or' functions of two variables can be done in as little as one time unit, in the VLsI model of computation.

#### 2.2 Correspondence to VLSi chips

The VLsI model of computation is designed so that VLsI chips correspond directly to communication graphs. This section details the way in which a communication graph is derived from any chip layout. The correspondences described here are necessarily vague, as the VLsI model of computation is intended to apply to any technology. Examples are taken from both the generalized MOS technology described by Mead and Conway [Mead 80], and from a "scaled" I <sup>2</sup>L technology [Evans 79].

For chips with a single layer of interconnection material, the correspondence is simple. Conductive paths on the surface of the chip are modeled as wires. Wire junctions and transistors are nodes. The topologies of the domains are nearly identical. The planar silicon substrate becomes the grid of unit squares of the lower THE VLSI MODEL OF COMPUTATION

PAGE 29

bound model. Chips with multiple layers of interconnection material are modeled by the technique shown on page 36.

*Conductors*, *wires*. Any VLsI chip must have an abstract operational description **in** terms of sequences of logical values that are carried along signal paths. Such a description exists at least in the chip designer's mind, when reasoning about the ways in which data is represented, modified, and moved.

A signal path is any conductor that serves to move data. Such conductors are modeled as wires in the VLSI model of computation. The data is modeled as a sequence of binary signals carried by the wires.

*Transistors, wire junctions, and nodes.* The wires of a communication graph have only two ends. A node is needed to model each spot on the chip where signals can fork ("fanout") or join ("fanin").

In particular, every active device or transistor on a chip is a node. In many **technologies, transistors** are **used for logical** fanin, as **illustrated** in Figure 2-5

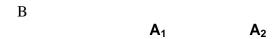

В

**Figure** 2-5: MOS circuit illustrating logic fanin at an active device, with corresponding communication graph.

**The output** C **goes to** ~'ld (logical I) whenever the transistor is nonconducting (B=O),

or whenever both A and B are at

A COMPLEXITY THEORY FOR VLSI

Transistors may also be the loci of logical fanout, as occurs in the I <sup>2</sup>L transistor of **Figure 2-6.**

В **В**

**Figure 2-6:** I <sup>2</sup>L circuit illustrating logic fanout at an active device, with corresponding communication graph.

Here, a logical  $\theta$  is a high impedance state, while a wire in the I state is nearly shorted to ground. The outputs  $C_I$  and  $C_2$  are  $\theta$  if the transistor is turned off, which happens only when the injector current is short-circuited through B.

Fanin and fanout can also occur without the mediation of an active device. For example, a single conductor can supply its signal to many different circuits. The model for such a conductor has a number of zero-delay fanout nodes, one for each fork in the signal path, as shown in Figure 2-7.

The fact that logic fanin can occur without an active device is perhaps surprising, yet it is a fairly common design practice. The I ~L nand gate of Figure 2-8 illustrates an appropriate model for conductors that perform logic.

In the VLsI model of computation, nodes are limited to four wires, so large fanouts and fanins must be modeled by multiple nodes. This should not pose any special difficulties, as nodes are only a square wire width in size. Nodes and wires can thus model the internal communication within a large active device, as shown in Figure 2-9.

Note that nodes are allowed to have rather complex functions, by the introduction of a large vector of state bits. A state vector is required for the definition of a source or sink node, but shouldn't be needed to describe the

**I** =-.B

THE VLSI MODEL OF COMPUTATION

**PAGE 31**

**Figure 2-7: MOS circuit** illustrating logic fanout **on a conductor,** with corresponding communication graph.

operation of any other node. **An exception arises** if the chip's conductorscarry more than two different logical signals. Nodes work only on binary signals, so they may need a few bits of state to model circuits employing multiple-valued logic.

Source and sink node correspondence will be treated in more detail later in this section.

**Power, grounch and synchronization.** A large proportion of the area of any VLSI chip is occupied by conductors that distribute power and global clock pulses. No wires are drawn in a communication graph to correspond to these conductors, since they do not carry information. This omission can only strengthen the lower bound results of this thesis, which are obtained without reference to the additional area constraints imposed by such wiring. Johannsen [Johannsen 78] treats the **problem of** power distribution on VLSI chips in more detail.

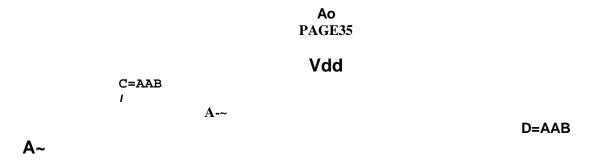

PAGE32  $\begin{array}{c} {}_{=}\text{-B } \lor \mathsf{A_3} \\ & \qquad \qquad \mathsf{A } \ \mathsf{COMPLEXITY } \ \mathsf{THEORY } \ \mathsf{FOR} \\ \mathsf{VLSI} \\ \mathsf{B_1} \\ & \qquad \qquad \mathsf{C} \ {}_{=}\ \mathsf{C_1} \lor \mathsf{C_2} \\ & \qquad \qquad = \ {}_{=}\ \mathsf{-(B_1 A B_2)} \end{array}$

**Figure 2-8: I** <sup>2</sup>**L** nand gate illustrating logic fanin on a conductor, with corresponding communication graph.

*Time*. The proper duration for a time unit is derived from the bandwidth limitation of wires, as expressed in assumption L2. A wire in a communication graph has at most unit bandwidth; the model's time scale must be adjusted until this assumption is satisfied.

mi C B<sub>2</sub> C<sub>1</sub> = B<sub>2</sub>

The effective bandwidth of a conductor on a chip is determined by the signal THE VLSI MODEL OF COMPUTATION

#### C4 = B

Figure 2-9: I <sup>2</sup>L transistor illustrating large fanout at a single device, with corresponding communication graph.

conventions employed by the VLSI designer, and the timing characteristics of the implementing technology. A signal convention is an association of a logical (boolean) value with a voltage range or current flow along a wire. A set of signal conventions thus provides a correspondence between the logical signals on the wires in a communication graph, and the dynamic electrical "states" of conductors on the surface of a VLSI chip. Each signal has a time dimension, in the sense that a changed voltage or current configuration must be maintained for some minimal duration of time before it amounts to a changed logical value.

The bandwidth of a conductor is the average information content of each signal divided by the duration of a signal. If each signal is equally likely to occur from the receiver's point of view, then the information content of each signal is the (base two) logarithm of the number of possible signals. Any other probability distribution for the signals gives a smaller information content and a smaller effective bandwidth. See [Shannon 49], p. 21.

The lower bound model of computation models the state of a wire as a binary variable, according to assumption L5. This leads to some difficulty in modeling circuits whose wires carry more than one bit per signal. For such circuits, the definition of the time unit is modified so that their wires have at most unit bandwidth. The unit of time for the lower bound model is accordingly set equal to the minimal duration of a signal on a wire, divided by the logarithm of the number

B B

PAGE 34 VLSI

#### A COMPLEXITY THEORY FOR

of such signals. Scaling the time unit in this way means that a signal carrying k bits of

information is modeled indirectly, by *k* one-bit transmissions.

The predominant two-valued logic is modeled directly. Signals in the model correspond one-to-one with signals on the chip. The unit of time is equal to the clock period, for synchronous logic. The effective time unit for an asynchronous circuit is usually determined by the rate at which data is fed to the circuit, but in any event it cannot be shorter than the delay through one stage of on-chip logic.

TTL-style "Tn-State" logic and other signal conventions with a high impedance state can also be modeled directly. The conductors in such circuits may send one bit of information in both directions simultaneously. Consider the "wire-anded" MOS circuit of Figure 2-10. The outputs C and D go to " $\sim$ d (logical I) if both A and B are low, placing their transistors in the high impedance state. The wire running between the two transistors must be carrying information in both directions, since C and D depend on both A and B. (If either C or D were unused, unidirectional information flow would suffice to model the circuit.)

Delay. In addition to the bandwidth constraint, time considerations enter the VLSI model in the form of wire delays. (Bandwidth is the amount of information emerging from the end of a wire in unit time, while delay is the amount of tim& that elapses between the transmission and receipt of a signal. Currently, VLsI wires can carry only one signal at a time, so that the delay of a wire determines its bandwidth. This may not always be the case.) According to assumption L5, a signal created at time t appears at the far end of a wire D at time ~ where ~D ~5 the non-negative delay of that wire. There is no explicit assignment of delay to each node, even though one could measure a delay from the time at which a signal appears at its inputs to the time at which a valid signal appears at its outputs. Such a "node delay" is of course an important component of the delay between the appearance of a signal at the input of one node and the appearance of a derived signal at the input of a connected node.

THE VLSI MODEL OF COMPUTATION

Figure 2-10: MOS "wire-and" circuit, with corresponding communication graph.

The delay of a VLsI conductor is often strongly dependent on its length. This is the reason that a separate delay is associated with each wire.

The delay situation on an actual VLSI chip is really quite complex. Circuit delays are not independent of signal conditions, as suggested by the fixed delays of the VLSI model. Circuits just do not respond to logical  $\theta$  and I signals at exactly the same rate. The previous state of the circuit is important, and even the states of the surrounding circuits and wires can materially affect delays. However, a single delay value should be quite sufficient to describe the logical design of any chip. (Small variances in delay times will not affect the behavior of a VLSI circuit, for timing variations are cancelled at each synchronization point. The clock period must of course be longer than the longest delay in the circuit.)

**C** 0 Bo **B**

**PAGE 36**

#### A COMPLEXITY THEORY FOR VLSI

It is expected that most chips can be modeled adequately with the following simplistic approach. Every wire emanating from a node that models an active logic element is assigned unit delay. Wires that connect to nodes that model wire junctions have zero delay.

*iviultiple layers of interconnection.The* embedding rules for communication graphs correspond directly to chips with a single layer of interconnection material. Wires are normally formed in this layer. Cross-overs are built with short runs in another conducting layer, for example, polysilicon in MOS technologies.

When modeling chips with a single layer of interconnection, the unit of length is just the minimal spacing between the centers of parallel conductors. The model's grid of unit squares describes this minimal conductor spacing precisely. At most one wire crosses the unit length edge of any square.

A legal communication graph can be drawn for every **VLsI** chip that employs multiple layers of interconnection by modifying the correspondence between surface area on the chip and unit squares of its graph. If there are k layers of interconnection, each unit of chip area is modeled by  $k^2$  unit squares. Figure 2-11 shows the way in which three units of chip area map into twenty-seven unit squares, if there are three layers of interconnection. The unit squares in each k-by-k image of a unit of chip area are numbered in a matrix notation, hut from bottom to top, left to right. Square (t) corresponds to the t layer on the chip. Transistors are formed in the first layer, and are thus drawn as nodes in squares (1,1). See Figure 2-

12. A conducting path running in the first layer of interconnection is modeled as a wire

running through squares  $\sim$  to get the connectivity right, it is also allowed to run through squares in row or column l. In general, wires formed in the ith layer of interconnection are drawn in squares (i,j) or  $(j, O \sim Connections)$  between adjacent layers of interconnection, or "vias," are drawn as wire bends in non-diagonal squares of a k-by-k image. For example, a bend in square (i,i+l) represents a connection between layers i and i and i and i branch or fork in a wire on layer i is modeled by a fanout node in square (i,j).

#### THE VLSI MODEL OF COMPUTATION

**PAGE 37**

# **Figure 2-11:** Correspondence scheme for a three-layer embedding. **Figure 2-12:** A communication graph occupying 9 units of surface area on a three-layer chip.

2

This correspondence scheme for drawing graphs from chips has an interesting implication for the reverse mapping. If a graph is known to require area A under the normal interpretation of a single level of interconnection, it also must require at least  $A/k^2$  area when k layers of interconnection are available. (Interpret the PAGE 38

A COMPLEXITY THEORY FOR VLSI

minimal embedding of the graph as  $A/k^2$  k-by-k images of unit areas.) The bound is not necessarily right: it may not be possible to embed the layout in exactly  $A/k^2$  area because of the added restrictions on the placement on nodes and wire bends in k-by-k images. (Also, as a practical matter, "vias" or connections between layers can not be placed arbitrarily close to each other.)

In the limit, the multiple level interpretation gives a "volume" result for graph embeddings. If a graph of area A is embedded in k=A  $1\sim 4$  levels, then it must occupy area  $A/k^2=A$  1,2. Assuming the levels are unit distance apart, the graph must fill an A  $1\sim 4$   $1\sim 4$   $1\sim 4$  unit cube, or A units of volume. This is a lower bound result, since the added restrictions on node and wire placement in kby-k images imply that some planar embeddings in area A do not correspond to legal A  $1\sim 4$  unit cube can be interpreted as an embedding in an A  $1\sim 4$   $1\sim 4$   $1\sim 4$  unit cube can be interpreted as an embedding in an A  $1\sim 4$   $1\sim 4$

*Input registers, source nodes.* Any VLSI chip that can solve an N-input problem must have N input registers to store the values of the input data. These input registers correspond to the source nodes of the communication graph for that chip.

Input registers appear as one of two structures on a chip, depending upon how information is stored. A bit of storage can be encoded as a static charge, or lack thereof, on a capacitive element. This approach is common in MOS technologies, in which the

gate of a transistor can serve as a storage capacitor. A bank of transistors may thus he an input register. Alternatively, the status of a current flow may define a bit. This dynamic representation is available in any technology. A positive feedback loop, or "cross-coupled logic," can make a circuit bistable. The state of such a circuit encodes one bit; a bank of them encodes an entire input value.

The conductors emanating from an input register correspond to wires coming out of a source node. This correspondence points up one difficulty with the representation of an input register by a single source node. An input register formed

THE VLSI MODEL OF COMPUTATION

PAGE 39

from a bank of storage cells is distributed in space and may have a large number of emanating conductive paths. A source node i~ localized to a unit square and can have only four outgoing wires. A more elaborate correspondence scheme is needed to handle this discrepancy.

The best model for a k-bit input register is a single source node connected to k-1 "auxiliary" nodes. Each node corresponds to one cell of the input register. Presumably, there are conductive paths linking the cells of the input register, so the nodes and wires of the model take up no more area than the input register. The conductive paths emanating from each cell of the input register may be directly modeled as wires connecting to the corresponding node.

This model will overestimate the time taken by the chip, if all the bits of the input register are transmitted immediately. This error is limited, however, to the k-I time units it takes for each of the auxiliary nodes to get its bit from the source node. Such an error is negligible in comparison with the total solution time for the problems treated here. In terms of the methodology presented at the beginning of this chapter, (A,T-K,p,N)-VLsI chips are a subset of (A,T,p,N)-communication graphs, although some (A,T,n,N)-VLsI chips lie outside of this set.

The VLsI model of computation can be extended to handle the case that problem input values are obtained from off-chip connections. A source node is drawn at the point of entry of each input value. On a VLsi chip, such a "point of entry" is a very large contact pad connected to an external wire. More than one input value may come through each contact pad, but there should be no trouble finding room for an equivalent number of source nodes in the image of a contact pad that is many hundreds of unit squares in area. A situation that causes a little more difficulty occurs when information about a single input value is obtained from several different contact pads (for example, the *kth* bit of each input variable might be received on the *kth* contact pad). Since all information about an input variable must be modeled as originating froni a single point, extra connections must be included in the communication graph between the images of contact

pads. In this way, the PAGE 40

#### A COMPLEXITY THEORY FOR VLSI

receipt of the *ku* bit of an input variable at a contact pad can be modeled by a signal from an on-chip wire, originating from the source node for that input variable. Fortunately, the data rate of an off-chip connection is comparable to the unit bandwidth of an on-chip wire [Mead 80], so that very few wires will be needed to model these imaginary connections between contact pads. Brent and Kung {Brent 79] model some of the aspects of off-chip communication in a more natural way.

Output registers, sink nodes. The N output values resulting from an on-chip computation must be stored in N output registers on the VLSI chip. The communication graph for such a chip has iV sink nodes, one for each of these output registers. The output register sink node correspondence is quite similar to that between input registers and source nodes. Output registers are implemented in the same way as input registers, as banks of storage cells.

When an output register is formed from a bank of k storage cells, it is modeled by a string of k-I auxiliary nodes and one source node. A maximal error of k-i time units can result, as was observed in the modeling of source nodes. This worst case arises if all output cells receive a bit of information in the last operation of the chip. The chip's computation is complete at that time, but the sink node of the model must collect a bit of information from each of the auxiliary nodes. Assuming they are connected linearly, this takes k-i time.

If problem outputs are to be shipped off-chip, sink nodes can be associated with contact pads in a manner analogous to the way in which source nodes were drawn for contact pads. Since a single sink node can handle many output variables, some aspects of the correspondence are simplified. However, connections between contact pads will still have to be introduced if different bits of a single output value are sent off-chip from different contact pads.

TFIEVLSI MODEL OF COMPUTATION

PAGE 41

#### 2.3Upper bounds

A communication graph is admissible if it can be implemented as a VLsi chip of the same area and time performance (within constant factors). The upper bound constructions of Chapter 4 are admissible communication graphs and hence correspond to feasible VLsI chips.

The upper bound model of computation consists of assumptions or admissibility rules Ui through U8. Any communication graph satisfying all these rules is admissible. Of course, such a graph must also satisfy assumptions Li through L8 to be a communication graph in the first place.

The upper bound assumptions were designed to be as simple and general as possible. Their simplicity stems largely from two decisions. All references to electrical parameters (capacitance, current density, etc.) are suppressed, and no attention is paid to constant factors in area or time calculations (the big-O notation is employed throughout). Of course some discussion of electrical and technological parameters is necessary to justify the upper bound assumptions. The constant factors will be largely ignored until Section 4.5, which estimates the actual size of the **VLsI** circuits proposed in Chapter 4.

The generality of the admissibility rules allows them to apply to all currently feasible **VLsI technologies. These include technologies based** on metal-oxide and Schottky-barrier field-effect transistors (e.g., the i'vlos family: CMOS, DMOS, 1-IMOS, **NMOS**, **PMOS**, ...) as well as the technologies based on bipolar transistors (such as I <sup>2</sup>L).

The first admissibility rule, assumption Ui, identifies and defines three types of nodes, *logic nodes, driver nodes*, and *receiver nodes*. These are drawn in Figures 2-13 and 2-14. The full text of the nile appears on page 44, in conjunction with its corresponding lower bound assumption, Li.

A logic node must fit in O(1) area, so it can not possibly have more than the O(1) connections allowed by assumption UI. Assumption U5, below, limits the state of a PAGE 42

Figure 2-13: Fanin, fanout and dimensions of a logic node.

Figure 2-14: Dimensions of driver and receiver nodes.

logic node to  $\theta(l)$  bits. Thus  $\theta(l)$  transistors suffice to implement the transmission function of any logic node. The transistors can all be minimum-sized, for they do not drive long wires. (The area of a transistor must be proportional to the length of the wire it drives. All wires have a parasitic capacitance that grows linearly with the length of the wire [Mohsen 791.)

When a logic node is actually implemented in VLsI, it will gate its outputs with a locally available clock pulse. The logic node will also need power and ground connections. As mentioned previously, this thesis assumes that some solution will be found for this distribution problem. However, there is no assumption that the phase of the clock signal will be constant over the entire surface of the Vi~si circuit, for that may be impossible to arrange. Other methods are necessary to synchronize distant circuits. Long-range synchronization is one of the functions of driver and receiver nodes.

0(1) 0(1)Receiver

THE VLSI MODEL OF COMPUTATION